RISC-V里程碑:192核处理器重磅亮相! 性能匹敌x86与ARM处理器

芯片设计领域初创公司VentanaMicroSystems近日宣布推出第二代Veyron系列基于RISC-V架构的全新处理器。据了解,全新VeyronV2是当今性能最为强大的RISC-V架构处理器,以Chiplet和IP的形式进行提供。VentanaMicroSystems是一家芯片设计领域的知名初创公司,该公司希望将数据中心和边缘计算市场CPU处理器从传统的基于x86和ARM架构的处理器,全面转移到基于开源指令集架构(ISA)——RISC-V架构的CPU处理器。

英特尔x86架构可谓耗费10多年的时间才在数据中心市场中占据了可观的份额,在智能手机应用端“打遍天下无敌手”的ARM架构至今仍然是数据中心圈层的边缘人物。在一些业内人士看来,也许开源指令集架构RISC-V可能仅仅需要五年的时间就能做到x86架构在数据中心领域已经做到的事情,这背后的逻辑主要在于大型科技企业以及大规模数据中心构建者们已经厌倦了无法控制自己的指令集架构基础以及在架构上花费高昂的成本。

VeyronV2——性能最强大的RISC-V架构处理器

在性能和效率方面,VeyronV2处理器可谓显着提升。数据显示,VeyronV2的性能提升高达40%。这种增益主要是通过显着的微体系架构增强、卓越的高性能处理器架构、增强化的缓存层次结构以及添加高性能矢量处理器而全面实现。

VeyronV2基于RISC-V架构处理器开发成本和上市时间全面缩短。VeyronV2chiplet采用业界领先的UCIechiplet互连,与前代产品一样,VeyronV2基于chiplet解决方案在单位经济性方面具有优势,可将处理器上市时间缩短两年,并将开发成本降低75%。基于chiplet的解决方案还通过调整计算、IO和内存的大小来提供更好的单元经济性。利用chiplet可组合架构使公司能够专注于创新和差异化,以实现工作负载全面优化。

此外,Ventana希望快速抓住并融入其VeyronV2核心设计的另一项重大变化是RISC-VVector1.0512位矢量扩展,该扩展类似于英特尔“Knights”XeonPhi处理器从2015年开始提供的扩展进程。这在一年前也刚刚添加到AMDGenoaEpyc处理器产品中。

Ventana为V2核心添加了扩展,使矢量引擎能够支持高密度矩阵运算,并允许客户将自身矩阵引擎添加到处理器架构之中,无论是在核心中还是在使用UCIExpress链路的离散chiplet中与之相邻。另外,V1核心没有任何矢量引擎或矩阵引擎扩展,这显然可能成为一个重要问题,因为许多基于人工智能的推理进程实际上仍在CPU端进行,在某些情况下,人工智能训练和HPC模拟和建模也在CPU上完成。

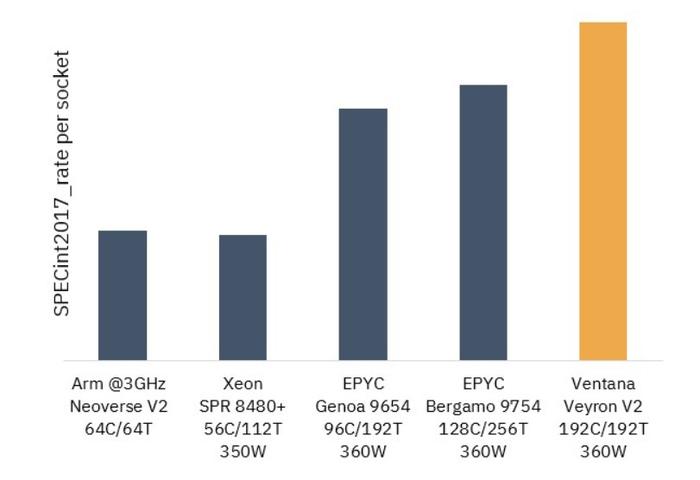

资料显示,VeyronV2核心将采用台积电的4nm工艺制程,四个V2chiplet可以与UCI-Express互连,以创建128个核心复合体,最多可将六个chiplet连接在一起,在单个Veyron插槽最高可获得192核。测评数据显示,在360瓦功率基准下,具有192个内核的Veyron2RISC-VCPU的整数吞吐量将比AMD的“Bergamo”Epyc9754处理器(具有128个内核和256个线程)高出约23%,在相同的360瓦热封装中,核心性能比96核AMD旗下GenoaEpyc9654高出约34%。

RISC-V架构是什么来头?

风靡全球的开源指令集架构——RISC-V,其在芯片设计领域的热度近年来火速攀升,一步步走向该领域的最核心地位,与ArmHoldings旗下的ARM和英特尔旗下x86两大主流架构一定程度上已形成三者鼎足之势。

RISC-V是一种完全开放的指令集架构(ISA),这意味着任何实体都可以免费访问和使用该技术。这种开放性使得RISC-V在学术界、初创企业和一些大型科技公司中都变得非常流行。由于RISC-V与ARM应用场景高度重合,均聚焦于低功耗和嵌入式场景,因此ARM是其最主要竞争对手,但近年来RISC-V开始被众多开发者用于数据中心领域,未来或将与x86架构一决高下,逐渐蚕食x86与ARM架构在各自擅长领域的份额。

RISC-V广泛用于学术研究、嵌入式系统、物联网(IoT)设备和一些数据中心的低功耗应用场景。由于其开放性和定制化属性,一些初创性的科技公司,甚至高通和谷歌这两大科技巨头正在将RISC-V用于创新性产品甚至可能用于旗舰产品。

RISC-V架构相比其他成熟的商业架构,最大的不同在于它是一个模块化的架构。因此RISC-V架构不仅短小精悍,而且其不同的部分还能以模块化的方式组织在一起,从而满足各种不同的终端应用场景。比如,RV32IC是一种精简指令集,适用于资源受限的嵌入式系统,如微控制器和嵌入式处理器,其中存储器带宽和功耗是关键关注点;而RV32IMFDC包括了更多的指令类型,适用于更广泛的应用领域,包括需要浮点运算指令和乘法/除法扩展指令支持的系统。

RISC-V架构的开放性和定制化属性使得更多的企业可以根据其特定需求进行定制化的处理器设计和制造,从而实现更适配的高性能以及功耗平衡。此外,企业采用RISC-V的成本相比于ARM架构和x86架构要低得多,并提高了应用可行性。总的来说,RISC-V架构在开放性和定制化方面相比于ARM架构具有极大的优势(尤其是成本优势),非常适合特定的应用终端以及定制化需求。

但是,聚焦于低功耗的RISC-V架构目前应用范围相对有限,尽管RISC-V在嵌入式系统和物联网等领域取得了相当大规模的成功,但要进入通用型的计算任务,以及高性能计算领域,还需要克服一些挑战。这些挑战包括性能和功耗与现有的服务器级x86和ARM处理器竞争、软件生态系统进一步扩展以支持高性能计算、以及在数据中心环境中广泛采用的过程和标准。

如果要在高性能场景中全面达到堪比x86架构处理器的竞争性水平,需要RISC-V贡献者们投入更多资源进行更深层次开发,并且需要在全球范围推动更多的软件开发商与RISC-V“打配合”。由于RISC-V是一个新兴的架构,不一定与现阶段主流软件兼容。这意味着在迁移到RISC-V平台上时,可能需要重新编译或修改一些应用程序。

RISC-V架构的参与力量越来越庞大

近期,RISC-V架构的市场参与力量可谓越来越庞大,其中不乏谷歌和高通等科技行业巨头。比如,汽车芯片领导者恩智浦、英飞凌以及美国移动端芯片巨头高通(Qualcomm)近日表示正在与一些欧洲汽车公司合作开发基于RISC-V架构芯片,以替代ARM芯片技术。

Alphabet旗下的谷歌(Google)近期表示,计划让全球最流行的移动操作系统安卓(Android)在基于RISC-V架构的芯片上运行(安卓和iOS两大手机操作系统目前均运行在基于ARM指令集的处理器上)。

来自高通的高管们在8月份表示,他们相信RISC-V架构将加速芯片行业创新步伐,并且改变科技行业。阿里巴巴可谓是RISC-V架构的重大贡献者,也是RISC-V架构集大成者之一,阿里已发布多款基于RISC-V架构的芯片,涵盖服务器、AI硬件和物联网等应用领域。

更重磅的消息在于,上述两大科技巨头——高通与Alphabet旗下谷歌正在基于RISC-V架构进行合作,推出一款基于RISC-V的可穿戴设备硬件解决方案,即RISC-V架构芯片,用于谷歌的WearOS智能手表操作系统。

高通表示,这种开源指令集架构将有助于为特定生态系统中的更多相关产品铺平道路,以充分利用基于RISC-V低功耗和高性能属性的定制化CPU。目前,高通计划在包括美国在内的全球范围内将基于RISC-V架构的可穿戴设备解决方案进行商业化推广。

EDA市场领导者新思科技近日更是官宣入局RISC-V架构,EDA软件是设计大规模集成电路必备的工具,堪称“芯片设计之母”。新思科技宣布扩展其ARC处理器IP产品组合,纳入全新RISC-VARC-V处理器IP,使客户能够从各种灵活、可扩展的处理器选项中进行选择,从而实现最佳的功耗性能效率。